FPGA Graphics: Part 7

Medium res graphics is here! At a resolution of 320x240, it is 4x the pixels as low res but still 1/4 the pixels of full res (640x480). It works much the same as low res but with a few tweaks. First, the x position is only divided by 2 instead of by 4. The y position is still divided by 4 though. For each row, of which there are 120, the same as low res, two lines get written. The first line of 40 bytes starting at 0 is written to even lines then the next 40 bytes starting at 128 (MSB is 1) is written to odd lines. It’s kind of confusing since there are 3 different “lines”.

Basically, the fpga will go through 480 hsync pulses before a vsync, so we can have at most 480 lines. This is the “ypos” in the module. This is then divided by 4 to get the row. This means ypos has to increase 4 times before the next row is loaded. However the second bit of the y position is used as the 8th bit in the read address. This bit changes every other ypos, so we still have 240 possible values. It had to be done this way because even though 240 fits inside 8 bits, and thus would be possible to use as the high address, the highest possible high address is only 159.

Even though the screen ram has a 16 byte address, it does not contain the full 65536 bytes, it only has 34000 since that’s the maximum needed to hold 640x480 bits. Because of this, 140 is the highest value that can be used. Anyway, using it is the same as using lowres except that you can write 40 bytes per line instead of 20, and when you move to the next line you first add 128 to the low address before incrementing the high address.

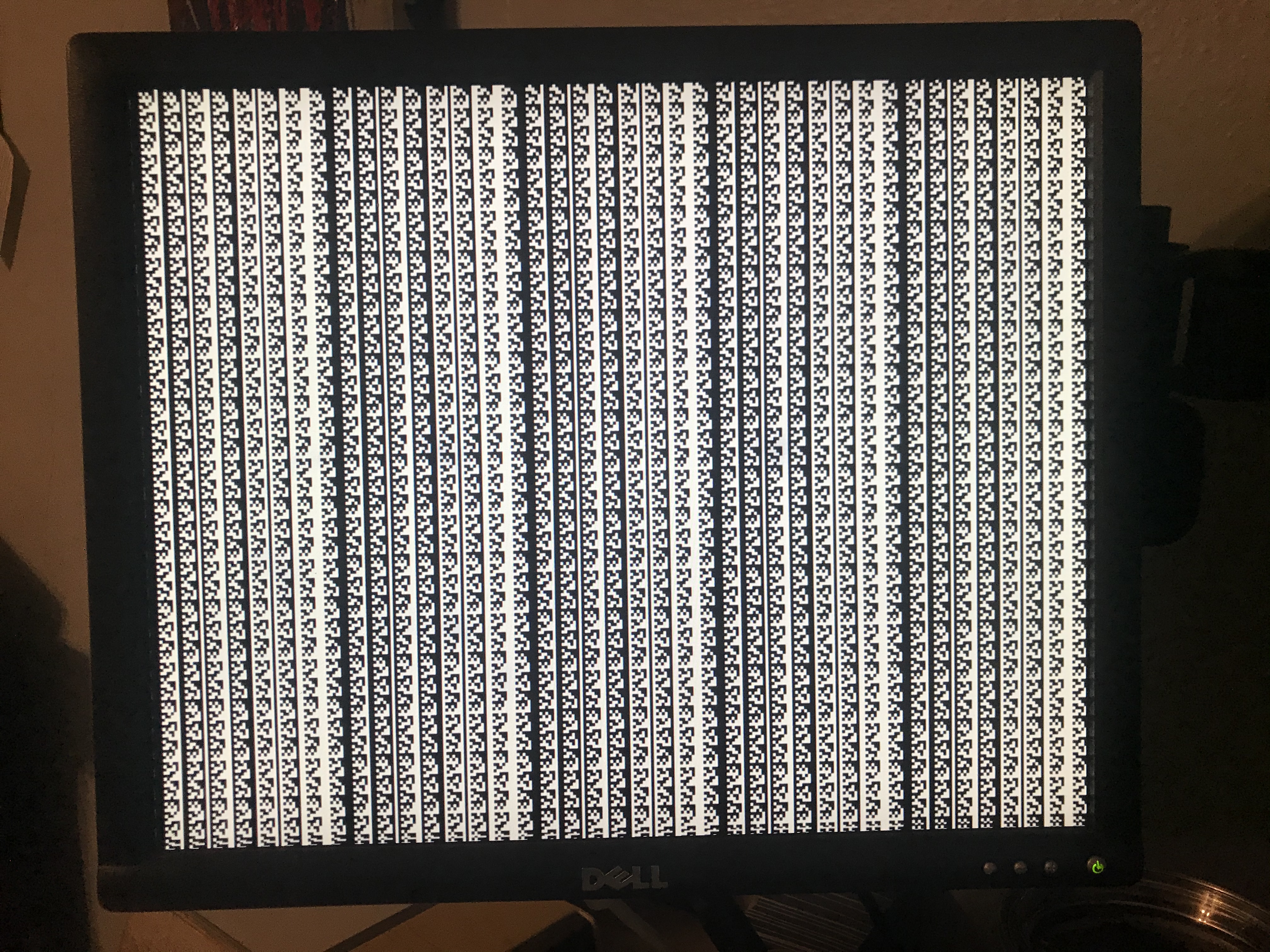

Here is a picture of the first test which writes the x position that the cpu is

writing to.

You can notice how every other line has bit 7 set. (The bits are displayed from

lsb to msb)

You can notice how every other line has bit 7 set. (The bits are displayed from

lsb to msb)

This next picture shows a counter counting from 0 to 255 then resetting.

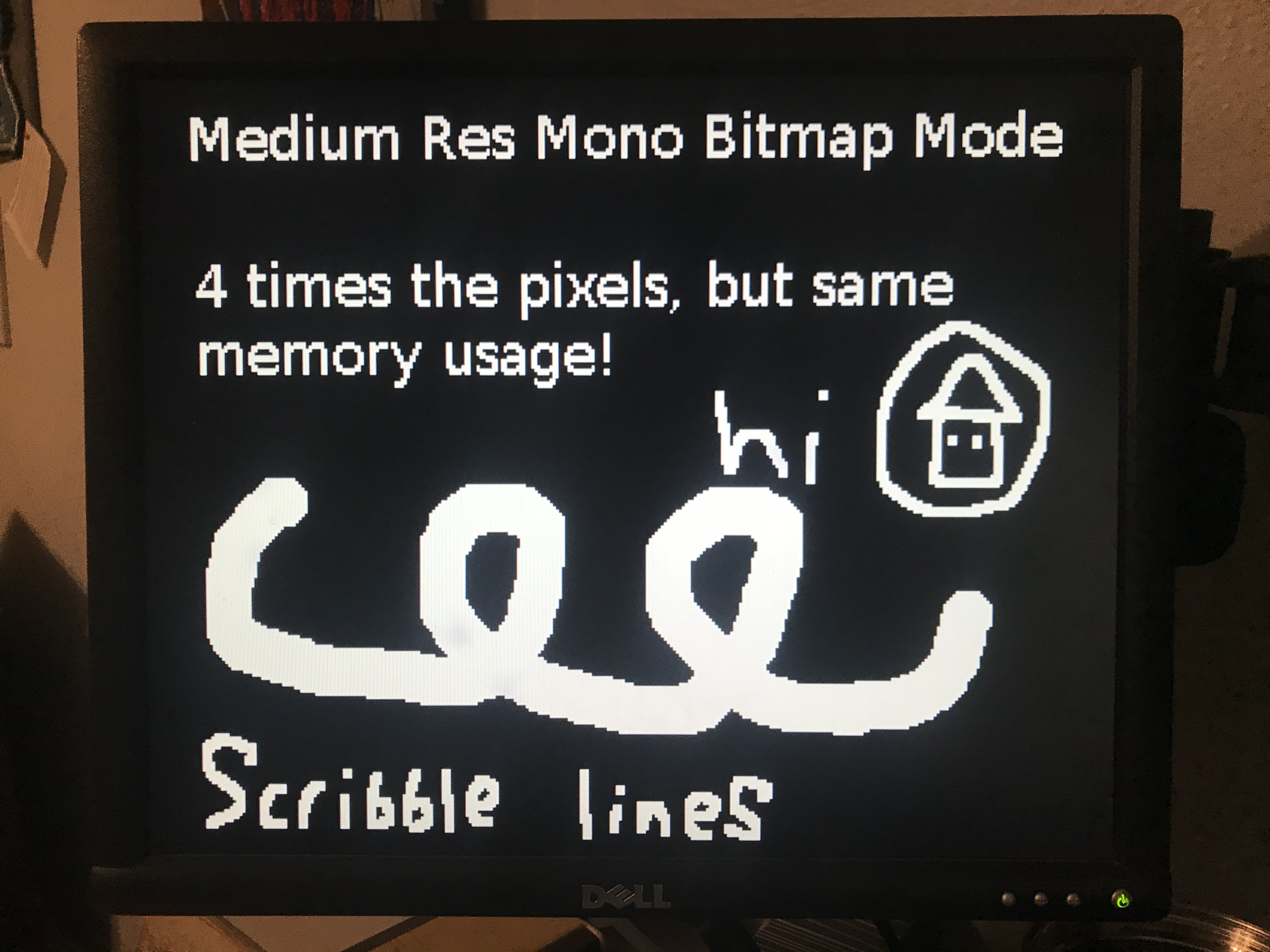

The final picture is a demonstration picture similar to the lowres one.

Next on the list is probably going to be a color bitmap mode, most likely lowres at first. Highres will come eventually but it will be more complicated and I don’t think a 6502 will be fast enough to use the whole screen anyway.

The FPGA code is on my gitlab here

The 6502 code is on my gitlab here