Efinix Trion FPGA with 6502

For the previous posts in this series, I have been using a DE10-Nano as the fpga board and the IO board that was given to us in ECE385 as the IO board. At some point though, I would like to make this a self contained circuit board to give me some experience designing an FPGA board. Unfortunately, due to chip shortages there are essentially no MAX10 FPGAs for sale, anywhere. Even if there were some in stock, they are actually somewhat expensive.

I considered using Xilinx instead, but I wasn’t a huge fan of their software, and I definitely was not a fan of its install size. I also took a look at a few of the smaller brands like microsemi and lattice, but again the software didn’t look great and I also wanted to have free IP, especially a memory controller.

In the end, I decided on a new brand called Efinix. It was kind of a gamble since you can’t actually try their software without buying a dev kit, and the cheap dev kits were not in stock, but it is actually pretty nice. Definitely lighter weight than the Quartus or Vivado, but not as terrible and text based as lattice diamond. That said, I did run into issues with libraries on linux that took a while to diagnose, and also the automatic PLL calculator doesn’t work anymore after I switched to i3 as my window manager from GNOME. Not sure why.

The downside of this is that I can’t use the IO board, and I also had to make a new CPU adapter board. The CPU adpter board was pretty easy and I whipped it up in KiCad and got it a few weeks later. At this point, I still have not made the IO board though, so any SD card action is going to have to wait until later. The T20F256 dev kit that I am using has many more headers that the DE10, but thats pretty much all it has. There are 3 buttons and 10 LEDs, but no switches or 7 segment displays, and no arduino compatible headers.

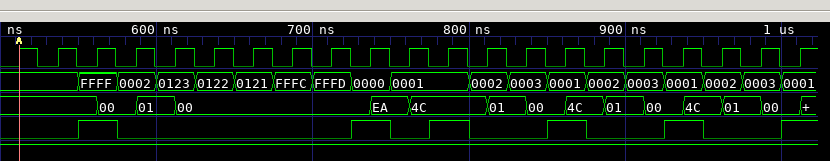

That said, it is still enough to get the CPU working. As before, the CPU is

essentially wired directly to the FPGA pins with nothing in between. On the

FPGA is a boot rom which contains an infinite loop, EA 4C 01 00. the EA at

the beginning is to show that the loop is running correctly, as the reset

vector will run the NOP while the loop will not.

That is pretty much it, here is the view from the logic analyzer, as well as a more stylized timing diagram.

Getting the block ram to work was kind of a pain. Efinity, the name of the Efinix IDE, has a built in IP browser and editor, but the bram IP is in beta and is distributed on their website as a zip file that you have to copy into your project, then run a few python scripts to configure it. Hopefully it will be more convenient to use in the future, but it works well enough for now.

Next I will work on getting the SDRAM working, and after that I can work on the IO board. Some of the things I want on the IO board are SDCard, USB, VGA/HDMI, Ethernet, PS/2, and USB Serial. That may be ambitious, but I want to build in as much functionality as I can.